Categorías

- Audio

-

Automóvil

- Actuadores

- Adaptadores

- Alarmas y GPS

- Amplificadores

- Antenas

- Arneses

- Bocinas Auto

- Cargadores Auto

- CB

- Conectores de Automóvil

- Convertidores de Impedancia

- Epicentros

- Extensiones

- Focos y Porta Focos Automotriz

- Frentes o Soportes para Autoestereo

- Fusibles y Porta Fusibles Automotriz

- Inversores

- Kits Instalación

- Módulos LED Automóvil

- Supresor de Ruido

- Switches Automóvil

- Terminales Auto

- Transmisores FM y Bluetooth

- Cables

- Celulares

- Computación y Redes

-

Energía

- Abanicos y Aire Acondicionado

- Baterías

- Cargadores

- Cinta de Aislar

- Clavijas, Contactos y Adaptadores

- Conectores

- Elevadores y Reductores

- Extensiones

- Focos y Porta Focos

- Fuentes

- Fusibles y Porta Fusibles

- Interlocks

- Multicontactos

- Probador de Voltaje y Corriente

- Reguladores de Voltaje

- Relevadores

- Switches

- Terminales

- Transformadores

- Timbres y Campanas

- Varistores y Termistores

- Ventiladores Energía

- Herramientas

- Iluminación

-

Proyectos y Robótica

- Adaptadores

- Aislantes y Soportes

- Arduino Genéricos

- Bases y Micas

- Baterías Robótica

- Buzzer

- Cajas para Proyectos

- Celdas Solares

- Conectores de Robótica

- Cristales

- Kits

- Engranes

- Extensiones de Robótica

- Carro Robot, Montajes

- Herramientas Proyectos

- Hoja de Símbolos o Master Circuit

- Imanes

- Joysticks

- Llantas

- Módulos

- Motores

- Optoelectrónica

- Pastilla Micrófonos

- Placas Circuito Impreso y Cloruro Férrico

- Potenciómetros y Presets

- Protoboard

- Raspberry

- Switches Proyectos

- Sensores

- Semiconductores

- Teclados

- Transformadores

- Wireless

- Semiconductores

- Tv y Video

- Telefonía

Artículos

Newsletter

Recibe promociones, descuentos y noticias.

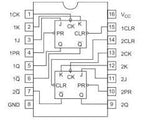

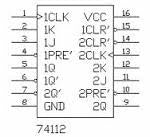

74LS112 TTL Dual J-K Flip-Flop With Preset & Clear

CIT74LS112

Descripción

- Totalmente amortiguado para ofrecer el máximo aislamiento de perturbaciones externas

- Calidad y fiabilidad

- Búffer completo para ofrecer el máximo aislamiento de las perturbaciones externas

- Aplicaciones: Comunicación y red

Especificaciones

- Familia: LS

- Tipo Flip-flop: JK

- Tipo de disparo: Edge Negativo

- Tipo de salida: Differential / Complementaria

- Tensión de alimentación mínima: 4.75 V

- Tensión de alimentación máxima: 5.25 V

- Retardo de propagación: 15 ns

- Frecuencia: 30 MHz

- Corriente de salida: 8 mA

- Temperatura de operación mínima: 0°C

- Temperatura de operación máxima: 70°C

- Encapsulado: DIP

- 16 pines

- Modelo: JJ2 +

Sustituto

Documentación

Uso

- Conectar la fuente de alimentación: Conecte la fuente de alimentación de 5 voltios al circuito.

- Conectar las entradas J, K y CLK: Conecte las entradas J, K y CLK a las señales de control que desee utilizar. Las señales de entrada J y K controlan la salida del flip flop, mientras que la señal de entrada CLK indica cuándo se deben actualizar las salidas.

- Conectar la entrada de reinicio asíncrona (CLR): Si desea reiniciar el flip flop a cero, conecte la entrada de reinicio asíncrona CLR a una señal de reinicio.

- Conectar la entrada de establecimiento asíncrono (PRE): Si desea establecer el flip flop en 1, conecte la entrada de establecimiento asíncrono PRE a una señal de establecimiento.

- Conectar las salidas Q y Q’: Conecte las salidas Q y Q’ del flip flop a los circuitos que desee controlar.

Es importante tener en cuenta que el 74LS112 Flip Flop JK es un dispositivo sensible al ruido y las fluctuaciones de voltaje, por lo que se debe tomar medidas para proteger el circuito y minimizar el ruido en el sistema. Por ejemplo, se pueden utilizar resistencias de pull-up o pull-down en las entradas para evitar que las señales floten cuando no están en uso. También se pueden utilizar filtros de ruido y decoupling capacitors para reducir el ruido en la fuente de alimentación.

Nota: El flip flop JK dual 74LS112 tiene dos entradas de reloj (CLK), dos entradas J y dos entradas K. Las entradas J y K son entradas de control que permiten establecer el estado de salida del flip flop. Los estados de salida serán:

- Si ambas entradas J y K están en nivel alto, la salida permanecerá en el estado anterior.

- Si la entrada J está en nivel alto y la entrada K en nivel bajo, la salida se establecerá en 1.

- Si la entrada K está en nivel alto y la entrada J en nivel bajo, la salida se establecerá en 0.

- Si ambas entradas J y K están en nivel bajo, la salida se invertirá.

El flip flop JK dual 74LS112 también tiene una entrada de reloj asíncrona (CLR) que puede reiniciar el estado del flip flop a cero si se activa. También tiene una entrada de reloj asíncrona (PRE) que puede establecer el estado del flip flop en 1 si se activa.

Productos Relacionados

-

74HC00D CMOS 4 Compuertas NAND ...

$ 8.00 -

74HC00P CMOS 4 Compuertas NAND ...

$ 17.00 -

74HC02D CMOS 4 Compuertas Posit...

$ 19.00 -

74HC02P CMOS 4 Compuertas Posit...

$ 19.00 -

74HC14D CMOS Seis Inversores Sc...

$ 10.00 -

74HC14N CMOS Seis Inversores Sc...

$ 21.00 -

74HC164N CMOS Registro de Corri...

$ 23.00 -

74HC27N CMOS Triple 3-Input NOR...

$ 49.00 -

74HC373D CMOS Ocho Compuertas T...

$ 24.00 -

74HC373N CMOS Ocho Compuertas D...

$ 29.00 -

74HC390N CMOS Decade Ripple Cou...

$ 60.00 -

74HC4050E CMOS Hex Buffer / Con...

$ 13.00 -

74HC423D CMOS Multivibrador Mono

$ 15.00 -

74HC573AN CMOS Octal D-Latch 3-...

$ 32.00 -

74HC595D,118 CMOS Registro de A...

$ 12.00 -

74HC595N CMOS Registro de Despl...

$ 10.00 -

74HC86D TTL Cuatro Compuertas O...

$ 14.00 -

74HCT08D,652 CMOS Compuerta Qua...

$ 19.00 -

74LS00 TTL 4 Compuertas NAND de...

$ 8.00 -

74LS01 TTL Cuatro Compuertas co...

$ 26.00 -

74LS02 TTL Compuerta NOR Cuádr...

$ 9.00 -

74LS03 TTL Cuatro Compuertas NA...

$ 35.00 -

74LS04 TTL Compuerta NOT con 6 ...

$ 8.00 -

74LS05 TTL Seis Inversores Col...

$ 28.00 -

74LS06 TTL Hex Inverter Buffer/...

$ 26.00 -

74LS07 TTL 6 Buffer/Driver C/Co...

$ 20.00 -

74LS08 TTL Compuerta AND con Do...

$ 8.00 -

74LS09 TTL Cuatro Compuertas AN...

$ 13.00 -

74LS09DR TTL Cuatro Compuertas ...

$ 38.00 -

74LS10 TTL Tres Compuertas NAND...

$ 14.00 -

74LS107 = 733W00103 TTL Dual J-...

$ 35.00 -

74LS109 TTL Dual J-K Flip-Flop ...

$ 35.00 -

74LS113 TTL Dual JK Negative Ad...

$ 19.00 -

74LS11D TLL Triple Compuerta AN...

$ 20.00 -

74LS11P TTL Triple Compuerta AN...

$ 12.00 -

74LS12 TTL Tres Compuertas NAND...

$ 18.00 -

74LS122 TTL Multivibrador Monoe...

$ 18.00 -

74LS123 TTL Multivibrador Monoe...

$ 38.00 -

74LS125 TTL Cuatro Buffer de Tr...

$ 25.00 -

74LS125AD TTL Cuatro Buffers de...

$ 19.00 -

74LS126 TTL Cuatro Buffers de B...

$ 64.00 -

74LS13 TTL Schmitt Trigers Dual...

$ 60.00 -

74LS132 TTL Cuatro Compuertas N...

$ 13.00 -

74LS133 TTL Entrada NAND con 13...

$ 35.00 -

74LS136 TTLCuatro Compuertas OR...

$ 20.00 -

74LS138 TTL Decodificador y Dem...

$ 46.00 -

74LS139P TTL Decodificador y De...

$ 29.00 -

74LS14 TTL Seis Inversores Schm...

$ 12.00 -

74LS145N TTL Manejador y Decodi...

$ 26.00

Comentarios