Categorías

- Audio

-

Automóvil

- Actuadores

- Adaptadores

- Alarmas y GPS

- Amplificadores

- Antenas

- Arneses

- Bocinas Auto

- Cargadores Auto

- CB

- Conectores de Automóvil

- Convertidores de Impedancia

- Epicentros

- Extensiones

- Focos y Porta Focos Automotriz

- Frentes o Soportes para Autoestereo

- Fusibles y Porta Fusibles Automotriz

- Inversores

- Kits Instalación

- Módulos LED Automóvil

- Supresor de Ruido

- Switches Automóvil

- Terminales Auto

- Transmisores FM y Bluetooth

- Cables

- Celulares

- Computación y Redes

-

Energía

- Abanicos y Aire Acondicionado

- Baterías

- Cargadores

- Cinta de Aislar

- Clavijas, Contactos y Adaptadores

- Conectores

- Elevadores y Reductores

- Extensiones

- Focos y Porta Focos

- Fuentes

- Fusibles y Porta Fusibles

- Interlocks

- Multicontactos

- Probador de Voltaje y Corriente

- Reguladores de Voltaje

- Relevadores

- Switches

- Terminales

- Transformadores

- Timbres y Campanas

- Varistores y Termistores

- Ventiladores Energía

- Herramientas

- Iluminación

-

Proyectos y Robótica

- Adaptadores

- Aislantes y Soportes

- Arduino Genéricos

- Bases y Micas

- Baterías Robótica

- Buzzer

- Cajas para Proyectos

- Celdas Solares

- Conectores de Robótica

- Cristales

- Kits

- Engranes

- Extensiones de Robótica

- Carro Robot, Montajes

- Herramientas Proyectos

- Hoja de Símbolos o Master Circuit

- Imanes

- Joysticks

- Libros

- Llantas

- Módulos

- Motores

- Optoelectrónica

- Pastilla Micrófonos

- Placas Circuito Impreso y Cloruro Férrico

- Potenciómetros y Presets

- Protoboard

- Raspberry

- Switches Proyectos

- Sensores

- Semiconductores

- Teclados

- Transformadores

- Wireless

- Semiconductores

- Tv y Video

- Telefonía

Artículos

Newsletter

Recibe promociones, descuentos y noticias.

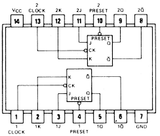

74LS113 TTL Dual JK Negative Adge-Triggered Flip-flop

CIT74LS113

Descripción

Circuito Integrado TTL 74LS113, Flip Flop JK negativo que ofrece entradas individuales J, K, con función de reset y clear. Este flip-flops doble está diseñados de modo que cuando el reloj pasa a ALTO, las entradas están habilitados y se aceptarán datos. El nivel lógico de la J y K entradas pueden ser autorizados a cambiar cuando el pulso de reloj es alta y la biestable llevará a cabo de acuerdo con la tabla de verdad, siempre y cuando la configuración mínima se observan veces. Los datos de entrada se transfiere a las salidas de la negativa continua borde del pulso de reloj.

- Totalmente amortiguado para ofrecer el máximo aislamiento de perturbaciones externas

Especificaciones

- Familia: LS

- Tipo de lógica: JK

- Tensión de alimentación mínima: 4.5 V

- Tensión de alimentación máxima: 5.5 V

- Corriente de suministro de energía: 6 mA

- Temperatura de funcionamiento mínima: -55°C

- Temperatura de funcionamiento máxima: 125°C

- Encapsulado: DIP

- 14 pines

Sustituto

NTE74113

Documentación

Productos Relacionados

-

Ventilador de Plástico 12V, 120...

$ 235.00 -

Transistor 2SD1251 TO220

$ 14.00 -

Transistor 2SC5027-O TO220

$ 14.00 -

Transistor 2SC5020 TO220

$ 14.00 -

Transistor 2SC4370 TO220

$ 12.00 -

Transistor 2SD315 TO220

$ 14.00 -

Transistor 2SD1406 TO220

$ 12.00 -

Juego de Engranes y Ejes

$ 65.00 -

Transistor 2SC1985 TO220

$ 35.00 -

Transistor 2SC1816 TO220

$ 25.00 -

Transistor 2SC1761 TO220

$ 22.00 -

Transistor 2SC1505 TO220

$ 18.00 -

Transistor 2SC1226 TO220

$ 29.00 -

Transistor 2SB856 TO220

$ 12.00 -

Transistor 2SB1342 TO220

$ 16.00 -

Transistor 2SB1366 TO220

$ 15.00 -

Transistor 2SB596 TO220

$ 16.00 -

Transistores 2SA770 TO220

$ 20.00 -

Transistores 2SA1837 TO220

$ 50.00 -

Transistor 2SC3293 TO220

$ 15.00 -

Módulo GPRS GSM SIM800 con Antena

$ 129.00 -

Transistor 2SC3229 TO220

$ 20.00 -

Transistor 2SC3183 TO220

$ 33.00 -

Transistor 2SC2491 TO220N

$ 33.00 -

Transistor 2SC1124 TO220N

$ 45.00 -

Transistor 2SB1299 TO220F

$ 20.00 -

Transistor 2SB1273 TO220

$ 16.00 -

Transistor 2SA671 TO220

$ 16.00 -

Transistor 2SA1601 TO220F

$ 42.00 -

Alcohol Isopropílico 250 ml

$ 95.00 -

Fuente de Alimentación Interio...

$ 620.00 -

Capacitor de Marcha 3.5 µF 250 VCA

$ 75.00 -

HEF40106BT 6 Inversores Schmitt...

$ 45.00 -

TNY264PN

$ 54.00 -

Multímetro Digital Profesional

$ 150.00 -

L7909CV

$ 15.00 -

Clavija Eléctrica Monofásica no...

$ 17.00 -

Switch Palanca 20A/125V 15A/250...

$ 220.00 -

Ventilador Metálico 24 V, 120 m...

$ 450.00 -

Jack Invertido 2.1 mm X 5.5 mm ...

$ 9.00 -

Relevador 12 V 30 A 1 Polo 1 Ti...

$ 290.00 -

LT11721N8

$ 230.00 -

Pegamento Adhesivo T-7000

$ 110.00 -

Módulo de 1 Relevador 12 V con ...

$ 79.00 -

XPT9911

$ 39.00 -

PIC16F54-I/P CMOS Microcontrola...

$ 45.00 -

Transistor NJW0281G Potencia

$ 70.00 -

Aire Comprimido Naceb 660 ml

$ 178.00 -

Convertidor OTG Micro USB-A a U...

$ 37.00

Comentarios